# **Chrontel CH7015 SDTV / HDTV Encoder**

### **Features**

- VGA to SDTV conversion supporting graphics resolutions up to 1024x768

- Analog YPrPb or YCrCb outputs for HDTV

- HDTV support for 480p, 720p and 1080i

- Macrovision<sup>TM</sup> 7.1.L1 copy protection support

- Programmable digital input interface supporting RGB and YCrCb input data formats

- TrueScale<sup>TM</sup> rendering engine supports under-scan in all TV output resolutions ¥

- Text enhancement filter ¥

- Adaptive flicker filter with up to 7 lines of filtering ¥

- Interlaced to progressive scan conversion for DVD

- Support for all NTSC, PAL and HDTV formats

- Support for SCART connector

- · Outputs CVBS, S-Video, RGB and YPbPr

- TV / Monitor connection detect

- Programmable power management

- Four 10-bit video DAC outputs

- Fully programmable through serial port

- Complete Windows and DOS driver support

- Low voltage interface support to graphics device

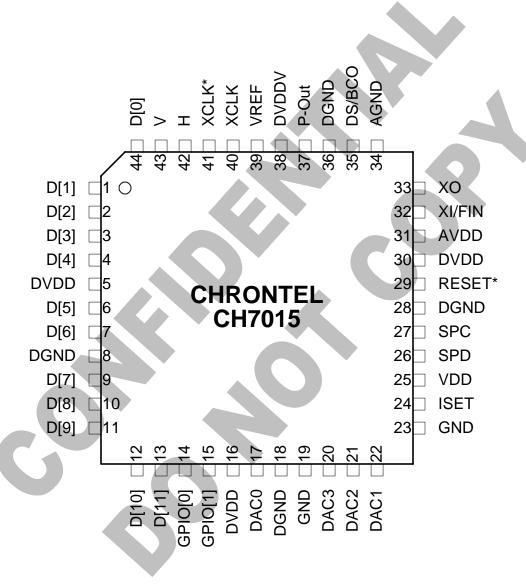

- Offered in a 44-pin LQFP package

#### 1.0 GENERAL DESCRIPTION

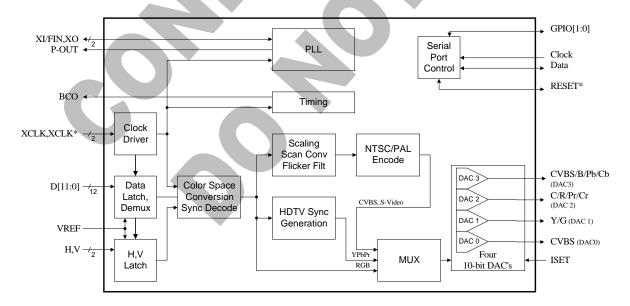

The CH7015 is a Display Controller device which accepts a digital graphics input signal, and encodes and transmits data through a 10-bit high speed DAC. The device is able to encode the video signals and generate synchronization signals for NTSC and PAL TV standards (SDTV), as well as analog HDTV interface standards and graphics standards up to UXGA. The device accepts data over one 24-bit wide variable voltage data port which supports 5 different data formats including RGB and YCrCb.

The TV-Out processor will perform non-interlace to interlace conversion with scaling and flicker filter, and encode data into any of the NTSC or PAL video standards. The scaling and flicker filter is adaptive and programmable to enable superior text display. Eight graphics resolutions are supported up to 1024 by 768 with full vertical and horizontal under-scan capability in all modes. A high accuracy low jitter phase locked loop is integrated to create outstanding video quality. Support is provided for Macrovision TM. CCIR-656 interlaced video can also be input and scan converted to non-interlaced video.

In addition to TV encoder modes, bypass modes are included which perform color space conversion to HDTV standards and generate and insert HDTV sync signals, or output VGA style analog RGB for use as a CRT DAC.

- † Patent number 5,781,241

- ¥ Patent number 5,914,753

Figure 1: Functional Block Diagram

#### 2.0 PIN ASSIGNMENT

**Disclaimer:** The information contained in this document is preliminary and subject to change without notice. Chrontel Inc. bears no responsibility for any errors in this document. Please contact Chrontel Inc. for design reviews prior to finalize your design.

### 2.1 Package Diagram

Figure 2: 44-Pin LQFP Package

209-0000-020 Rev. 0.1, 11/08/2001

# 2.2 Pin Description

**Table 1: Pin Description**

| Pin #                       | # of<br>Pins | Туре   | Symbol                     | Description                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----------------------------|--------------|--------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1-4,<br>6-7,<br>9-13,<br>44 | 12           | In     | D[11]-D[0]                 | Data[11] through Data[0] Inputs These pins accept the 12 data inputs from a digital video port of a graphics controller. The levels are 0 to DVDDV, and the VREF signal is used as the threshold level.                                                                                                                                                           |  |  |  |  |  |

| 14-15                       | 2            | In/Out | GPIO[1:0]                  | General Purpose Input - Output[1:0] (waek internal pull up) These pins provide general purpose I/O controlled via the serial port. Th allows an external switch to be used to select NTSC or PAL at power-up. internal pull-up will be to the DVDD supply.                                                                                                        |  |  |  |  |  |

| 17                          | 1            | Out    | CVBS<br>(DAC0)             | Composite Video This pin outputs a composite video signal capable of driving a 75 ohm do terminated load. During bypass modes this output is valid only if the data format is compatible with one of the TV-Out display modes.                                                                                                                                    |  |  |  |  |  |

| 20                          | 1            | Out    | CVBS/B/Pb<br>/Cb<br>(DAC3) | Composite Video / Blue / Pb / Cb Output This pin outputs a selectable video signal. The output is designed to drive 75 ohm doubly terminated load. The output can be selected to be compos video, blue (for SCART type 1 connections), the Pb component of YPrPb the Cb component of YCrCb.                                                                       |  |  |  |  |  |

| 21                          | 1            | Out    | C/R/Pr/Cr<br>(DAC2)        | Chroma / Red / Pr / Cr Output This pin outputs a selectable video signal. The output is designed to drive a 75 ohm doubly terminated load. The output can be selected to be s-video chrominance, red (for SCART type 1 connections), the Pr component of YprPb or the Cr component of YCrCb.                                                                      |  |  |  |  |  |

| 22                          | 1            | Out    | Y/G<br>(DAC1)              | Luma / Green Output This pin outputs a selectable video signal. The output is designed to drive a 75 ohm doubly terminated load. The output can be selected to be s-video luminance or red (for SCART type 1 connections).                                                                                                                                        |  |  |  |  |  |

| 24                          | 1            | In     | ISET                       | Current Set Resistor Input This pin sets the DAC current. A 140 ohm resistor should be connected between this pin and GND (pin 23) using short and wide traces.                                                                                                                                                                                                   |  |  |  |  |  |

| 26                          | 1            | In/Out | SPD                        | Serial Port Data Input / Output This pin functions as the data pin of the serial port, and uses the DVDD supply.                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 27                          | 1            | In     | SPC                        | Serial Port Clock Input This pin functions as the clock pin of the serial port, and uses the DVDD supply.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 29                          | 1            | In     | RESET*                     | Reset * Input (Internal pull-up) When this pin is low, the device is held in the power-on reset condition. When this pin is high, reset is controlled through the serial port.                                                                                                                                                                                    |  |  |  |  |  |

| 32                          | 1            | In     | XI / FIN                   | Crystal Input / External Reference Input A parallel resonance 14.31818MHz crystal (± 20 ppm) should be attached between this pin and XO. However, an external CMOS compatible clock can drive the XI/FIN input.                                                                                                                                                   |  |  |  |  |  |

| 33                          | 1            | Out    | XO                         | Crystal Output A parallel resonance 14.31818MHz crystal (± 20 ppm) should be attached between this pin and XI / FIN. However, if an external CMOS clock is attached to XI/FIN, XO should be left open.                                                                                                                                                            |  |  |  |  |  |

| 35                          | 1            | Out    | ВСО                        | Buffered Clock Output This output pin provides selectable buffered clocks to be output, driven by the DVDD supply. The output clock can be selected using the BCO register.                                                                                                                                                                                       |  |  |  |  |  |

| 37                          | 1            | Out    | P-Out                      | Pixel Clock Output  This pin provides a pixel clock signal to the VGA controller which can be used as a reference frequency. The output is selectable between 1X or 2X of the pixel clock frequency. The output driver is driven from the DVDDV supply. This output has a programmable tri-state. The capacitive loading on this pin should be kept to a minimum. |  |  |  |  |  |

| 39                          | 1            | In     | VREF                       | Reference Voltage Input The VREF pin inputs a reference voltage of DVDDV / 2. The signal is derived externally through a resistor divider and decoupling capacitor, and will be used as a reference level for data, sync and clock inputs.                                                                                                                        |  |  |  |  |  |

209-0000-020 Rev. 0.1, 11/08/2001 3

| Pin#       | # of<br>Pins | Type   | Symbol         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------|--------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 40-41      | 2            | In     | XCLK,<br>XCLK* | External Clock Inputs  These inputs form a differential clock signal input to the device for use with the H, V and D[11:0] data. If differential clocks are not available, the XCLK input should be connected to VREF.  The clock polarity used can be selected by the MCP control bit.                                                                                                                                                                                       |  |  |  |  |

| 42         | 1            | In/Out | Н              | Horizontal Sync Input / Output  When the SYO control bit is low, this pin accepts a horizontal sync input for use with the input data. The amplitude will be 0 to DVDDV, and the VREI signal is used as the threshold level. This pin must be used as an input in all bypass modes.  When the SYO control bit is high, the device will output a horizontal sync pulse, 64 pixels wide. The output is driven from the DVDD supply. This output is valid with TV-Out operation. |  |  |  |  |

| 43         | 1            | In/Out | V              | Vertical Sync Input / Output When the SYO control bit is low, this pin accepts a vertical sync input for use with the input data. The amplitude will be 0 to DVDDV, and the VREF signal is used as the threshold level. This pin must be used as an input in all bypass modes.  When the SYO control bit is high, the device will output a vertical sync pulse one line wide. The output is driven from the DVDD supply. This output is valid with TV-Out operation.          |  |  |  |  |

| 5,16,30    | 3            | Power  | DVDD           | Digital Supply Voltage (3.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 8,18,28,36 | 4            | Power  | DGND           | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 38         | 1            | Power  | DVDDV          | I/O Supply Voltage (1.1V to 3.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 31         | 1            | Power  | AVDD           | PLL Supply Voltage (3.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 34         | 1            | Power  | AGND           | PLL Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 25         | 1            | Power  | VDD            | DAC Supply Voltage (3.3V)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 19,23      | 2            | Power  | GND            | DAC Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

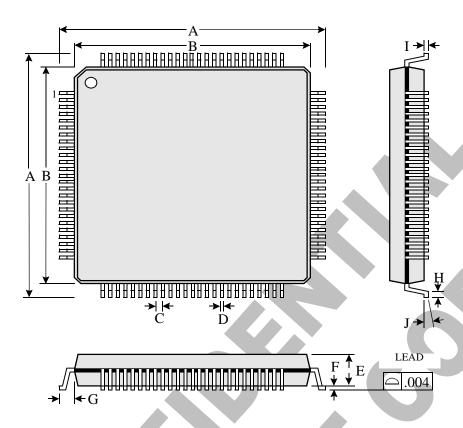

## 3.0 PACKAGE DIMENSIONS

**Table of Dimensions**

| No. of Leads    |    | SYMBOL |      |      |      |      |      |      |      |            |  |  |

|-----------------|----|--------|------|------|------|------|------|------|------|------------|--|--|

| 44 (10 X 10 mm) | A  | В      | С    | D    | E    | F    | G    | Н    | I    | J          |  |  |

| Milli- MIX      | 12 | 10     | 0.80 | 0.30 | 1.35 | 0.05 | 1.00 | 0.45 | 0.09 | <b>0</b> ° |  |  |

| meters MAX      | 12 |        |      | 0.40 | 1.45 | 0.15 |      | 0.75 | 0.20 | <b>7</b> ° |  |  |

209-0000-020 Rev. 0.1, 11/08/2001

2210 O'Toole Avenue, Suite 100 San Jose, CA 95131-1326 Tel: (408) 383-9328 Fax: (408) 383-9338

www.chrontel.com E-mail: sales@chrontel.com

©2001 Chrontel, Inc. All Rights Reserved.

Chrontel PRODUCTS ARE NOT AUTHORIZED FOR AND SHOULD NOT BE USED WITHIN LIFE SUPPORT SYSTEMS OR NUCLEAR FACILITY APPLICATIONS WITHOUT THE SPECIFIC WRITTEN CONSENT OF Chrontel. Life support systems are those intended to support or sustain life and whose failure to perform when used as directed can reasonably expect to result in personal injury or death. Chrontel reserves the right to make changes at any time without notice to improve and supply the best possible product and is not responsible and does not assume any liability for misapplication or use outside the limits specified in this document. We provide no warranty for the use of our products and assume no liability for errors contained in this document. Printed in the U.S.A.

6 11/08/2001 209-0000-020 Rev. 0.1,